Table of Contents

As you might have heard, Framework, the company behind highly-repairable and Linux-compatible laptops, has just made a new motherboard available for its main product, the Framework Laptop 13. Up to now, nothing crazy or out of the ordinary - Framework maintains their laptops well-supported and has a long history of delivering on making CPU platform upgrades over time; but this is something that does not quite pack the same punch for now, but that every Linux and free software enthusiast should definitely be excited about. This new motherboard, in fact, is based on the RISC-V architecture.

What about RISC-V?

Technically speaking, RISC-V itself is not a CPU, but an Instruction Set Architecture - in short, ISA, that also happens to be completely free and open source. To understand what this means properly, though, we'll need to backtrack for a second, and get an idea about how CPUs work. If you already have a basic background in this area, feel free to skip ahead to the next section.

What is an ISA?

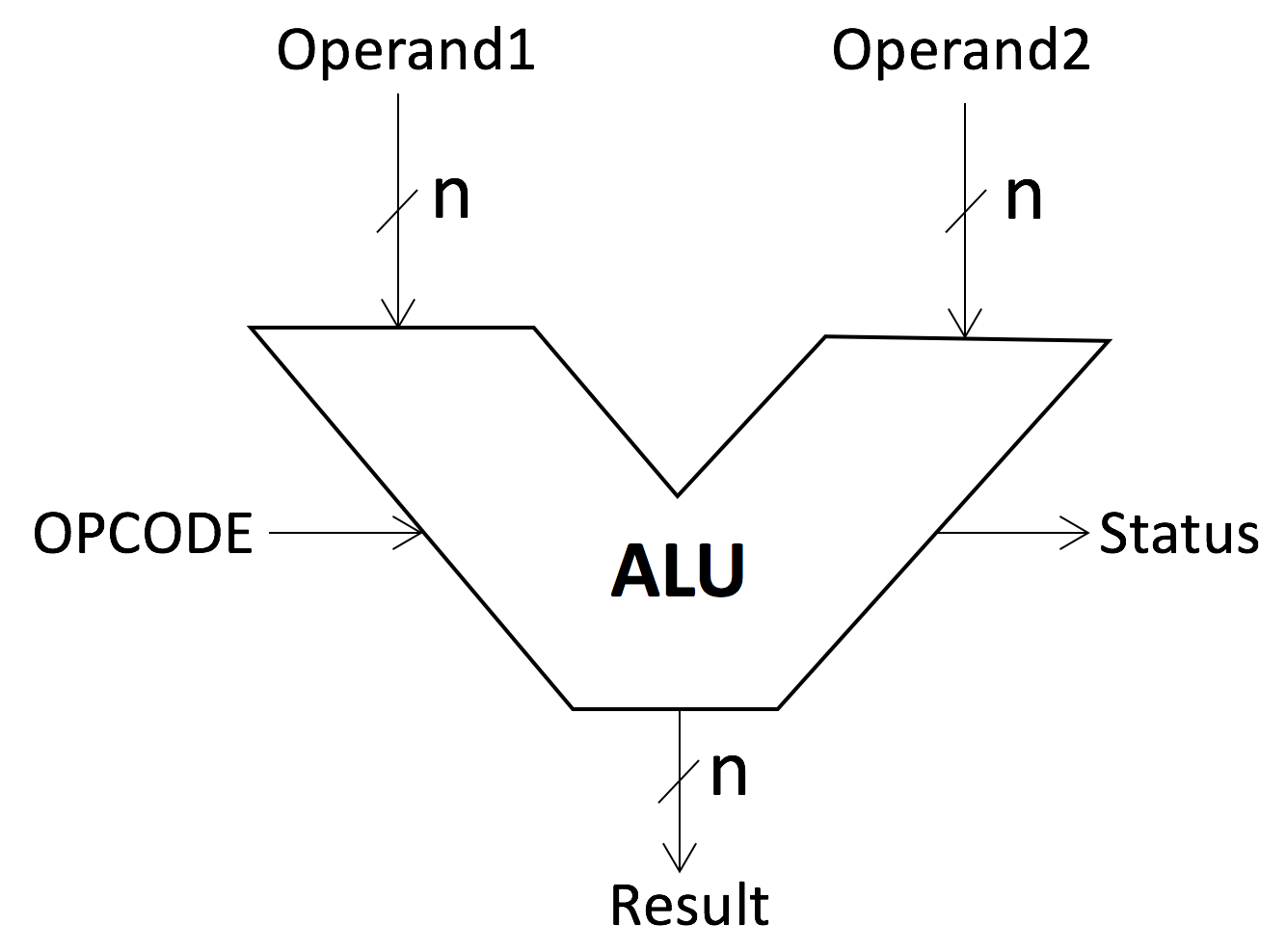

As you know, the main component in a computer system can be considered the CPU, the Central Processing Unit, also known as the "Processor". It is easily the most important thing that's on your motherboard, as it is the component that runs instructions and makes arithmetic and logical calculations all the time to make any computer work.

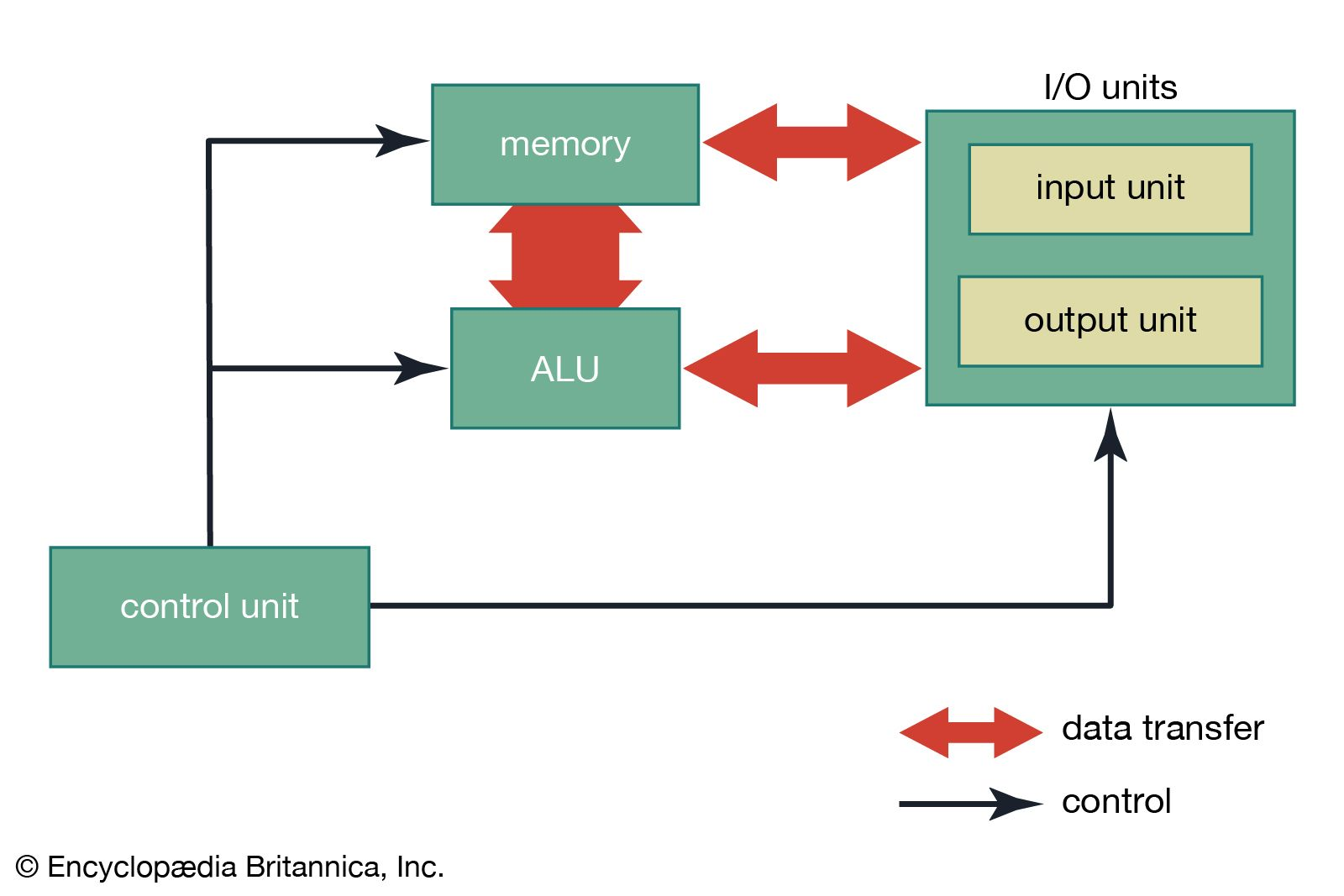

While modern CPU's are pretty complex, and exist within the context of a System-on-Chip (which we will talk about more in detail later), every CPU shares the same fundamental blueprint and components:

- The main part of the CPU is the Arithmetic and Logic Unit, ALU for short. It's the piece of circuitry that actually computes all the mathematical operations that are required for your computer to work.

-

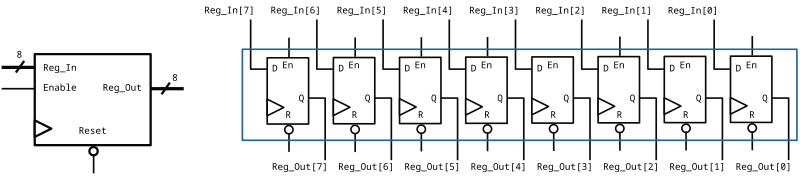

The registers, a memory location that is integrated in the CPU and that can be used to briefly store values, such as the inputs or the result of a mathematical operation executed by the ALU

-

The Control Unit, "CU" for short, which is the component that acts a bit like an Orchestra director for your CPU. It fetches the next instruction to run from memory, it decodes it in order to figure out how it needs to be executed, and then it executes it; for example, feeding the operands for an operation to the ALU, and having it compute the result.

But what about these instructions? What kinds of instructions can a CPU execute? How are they defined? This is where the ISA comes in. The Instruction Set Architecture is a model that defines all aspects of how this works: it enumerates all the instructions that a CPU supports and everything related to them, such as the data types they accept as input and produce as output, the registers that they use and how they use them, and how a lot of other basic functionality like memory handling and I/O works. Unlike all the other components we have previously seen, though, the ISA is not a physical entity that is made of transistors - it is an abstract, theoretical model that defines how a CPU works.

So, what is RISC-V?

With the basic context out of the way, what is RISC-V? RISC-V is an ISA that is completely free and open source. Purely due to this, it fills an important position, as it is one of the very few ISAs that are not proprietary. Unless you are running on a RISC-V computer or something similar, though, you are currently using a CPU that has a closed-source ISA: it should be an Intel or an AMD processor, or some kind of ARM SoC. What this means is that, except for some basic facts about the architecture that have been documented by the chip-maker, you do not know how it really works and you cannot create your own compatible version on the same ISA, since you are not licensed to do that. Even if you could, the specifics on how exactly to achieve that are tied to a trade secret, and are someone else's intellectual property.

This changes with RISC-V. The open ecosystem around it makes it the perfect candidate for completely free hardware that you can use, study, modify and redistribute freely, without fees or restrictions, in the same spirit Linux is distributed under. In fact, the related documents are provided under a Creative Commons License or a BSD license - it's free as in freedom, public domain.

This is a big deal. We have already seen that an ecosystem is worth more than the sum of its parts, and that the collaborative nature of open source ecosystem makes technological process flourish: just look at the Linux ecosystem, perhaps one of the healthiest ecosystems around, and home to the one piece of software that is likely to outlive us all.

In RISC-V land, a hardware manufacturer can start designing IC (Integrated Circuits) that implement the RISC-V ISA specification, and add their own extensions around it - things like PCIe and USB bus connectivity - as well as do their own experimentation on additions to the ISA. Individual players are encouraged to submit proposals for improvements to an official RISC-V board, who helps evaluate the proposals and make the ones who are found to be a good fit with the project direction to be included in future versions of the ISA. This collaborative environment closely mirrors that of the early days of computing: it's exciting, and it fosters growth. One chip manufacturer can find a performance improvement or another enhancement and, if it's a good one, then all the other manufacturers have access to it. This is exactly what helped make the RISC-V Framework Laptop a reality: a company had been building ICs around RISC-V, and they ultimately were able to provide the cores that power the board itself.

This is a great balance: while it's not quite the far west - there is no guarantee that your change will be approved upstream - it is still leaps and bounds better than what happens on ARM land, where the ARM company owns the ISA, and licensed hardware manufacturers have little freedom on what to do with it. This climate is the opposite of collaboration and, rather than fostering growth, it often fosters drama and disagreement. A good example of this is that fact that we are still talking about the rocky relationship between ARM and Qualcomm - two companies within the same ecosystem that are in a weird dynamic where they can't seem to get along, but they are symbiotic to each other's growth. It is also incomparably more open than the reality in x86-land, which is fundamentally a duopoly between Intel and AMD.

Another advantage over ARM is that commercial ARM boards are often very locked down, requiring proprietary drivers to be able to work properly, and very often shipping with locked bootloaders that prevent the installation of other operating systems. Remember when we talked about the Snapdragon X Elite back in August? In retrospect, I might have been a little bit too optimistic: Linux support on that chip is not panning out well to say the least, as Qualcomm has been really dragging their feet on their original Linux support promises, making the Linux experience on the X Elite largely a no-go, several months after release. Never has any Intel or AMD laptop chip been in such a rocky state Linux-support wise after this much time for a very long time. Qualcomm has been facing a lot of challenges on the ARM for Windows side of things - the part of the X Elite project where the money really is, and where there is a binding contract with Microsoft to fulfill - and it seems like Linux has been a second thought since then. Radio silence on Tuxedo's promised ARM-based laptop as well: it's just not panning out. By sheer contrast, Linux support on RISC-V platforms is amazing, and support for those platforms gets upstreamed quickly.

As a consumer, RISC-V means you get more freedom from choice - real choice, without gatekeepers like ARM. As a power user, it means that you are no longer merely an user of your hardware platform, but you are also potentially a developer or a designer: you are free to tinker, research, and contribute your findings back upstream for everybody's benefit, doing science like it was meant to be done. As a Linux user, it means that you will be getting amazing platform support, where Linux is finally the first-class citizen rather than an afterthought that gets some of the features destined to Windows systems much later if ever - something that happens more often on other platforms - resting assured that the upstream kernel will be enough to run your SoC just fine, with no need to fetch a patched kernel, or load proprietary modules.

RISC-V is not only interesting for consumer hardware, though. In fact, its growth is becoming increasingly attractive for the High-Performance Computing field, prompting a slew of research around how RISC-V could fit in performance computing, like this brand new August 2024 paper titled "Evaluating ARM and RISC-V Architectures for High-Performance Computing with Docker and Kubernetes", which explores with great detail just how promising this architecture it for serious workloads, though it still needs some time in the oven.

Meaning of the RISC-V name

But why is RISC-V called RISC-V?

First of all, RISC-V is a Reduced Instruction Set Computer - RISC.

An ISA can either be a Reduced or Complex Instruction Set Architecture.

- The most common home computers, based on the x86 family of processors, of which the most important players are Intel and AMD, have a Complex Instruction Set Architecture, CISC for short. What it means is that their ISA contains a large number of different instructions, each of which can be very powerful and represent the equivalent of running several simpler instructions consecutively. This allows the ISA to be very expressive.

- Imagine we are in the 60's. Still well in the beginning of computation, and we are still mostly figuring out the best way to trick rocks into thinking. There are several limitations to keep into account, such as that computers have very limited amounts of memory, so programs must be very small and simple.

- The advantage to this approach is that the instruction set already directly targets several high-level programming concepts like calls and loops, making writing Assembly code - the code that represents sequences of hardware instructions the CPU must execute in batch - potentially more comfortable, allowing programmers to collapse what would be several lines of code into just one.

- As a result, this approach allowed programmers to create smaller Assembly programs, which used to be a big deal back in the 60's, where computers were much more memory-constrained compared to today.

- If up to this point it looked too good to be true, that's because it was. Later on, it turned out that using complex instructions often didn't translate into the best performance, but it was possible to drastically speed up several programs by ignoring the big, high-level instructions and using batches of small ones instead. This happened for several reasons, one of which being the fact that CPU manufacturers were so obsessed with making Assembly programs shorter that the CPU microcode began to expose instructions that the CPU could not operate efficiently and quickly: programmers didn't know that though, so they would use them anyway, blissfully unaware of how that single advertised processor operation actually costed.

- The RISC approach takes the opposite idea. RISC is what ARM processors, like the one in your phone, use - as well as RISC-V itself.

- We are now more in the 70's and 80's. Some of the shortcomings of CISC have been acknowledged, and we are no longer as memory-constrained as we were a decade back. We can finally afford to run some slightly larger programs.

- The idea behind RISC is to really simplify the ISA. Only basic, primitive operations are included, where each instruction takes a fixed size, and the same thing a line of CISC code achieved required several lines of simpler RISC instructions. RISC operations do not perform more than one thing, and different instructions are separate in scope.

- With this paradigm, performance is great. RISC computers can enjoy few simple addressing modes, all the instructions are of about the same size and length, and they all take roughly the same ballpark of time to complete, making execution times much more predictable, which allows design simplification, which often translate in even better performance in a vicious cycle.

- Many RISC-based computers came and went, but CISC reigned supreme in most home computers and servers for a while, mostly due to compatibility reasons with software previously written for CISC processors, especially on the Windows platform. However, RISC has been making a comeback with ARM, because of its highly performant and power-efficient nature, that makes ideally better than CISC for most use cases, while also making it possible to achieve good performance while running in incredibly constrained environment and embedded devices, like smartphones, still managing to get incredibly good performance, drastically more efficiently, so, with significantly less heat to dissipate, finally allowing for passive cooling to be viable in a lot of situations.

So, there we have it. RISC-V is called like that because it's a RISC ISA. But why V?

Brief history of RISC-V

Towards the 90's, the benefits of RISC-V triggered some academic curiosity, which itself birthed the publication Computer Architecture: A Quantitative Approach, co-authored by David Patterson, who later participated in RISC-V. This publication was a RISC ISA called DLX, which was more of a "toy" architecture meant for educational use.

In 2010, the same David Patterson decided to aid UC Berkeley academic Krste Asanović, who wanted to create an open-source operating system as a short side-project involving some graduate students. That is how the Berkley RISC ISA was born. The small side project that was meant to only last for about three months turned out not to be so small, and it went through five different iterations. RISC-V is the name it took at its fifth iteration, after being officially introduced on August 6, 2024.

Well, does this not remind us of something? Linux, too, was meant to be a short hobby project, never meaning to be big or anything like that. This is another time that a side project grew way out of scope and became a very big deal.

Why is it important?

As more time passed, the writing on the wall was clear: RISC-V has started proving itself as a viable platform, and it has started spreading like wildfire among tinkerers and researchers due to its open-source nature, which actively encourages development, rather than prohibiting it.

While adoption is still in its early stages, RISC-V already exists commercially in several embedded chips: for example, those of you who are reading on a Framework laptop - yes, the regular CISC one - are actually using a tiny RISC-V chip every day, every time they unlock their laptop by tapping their finger on the fingerprint reader!

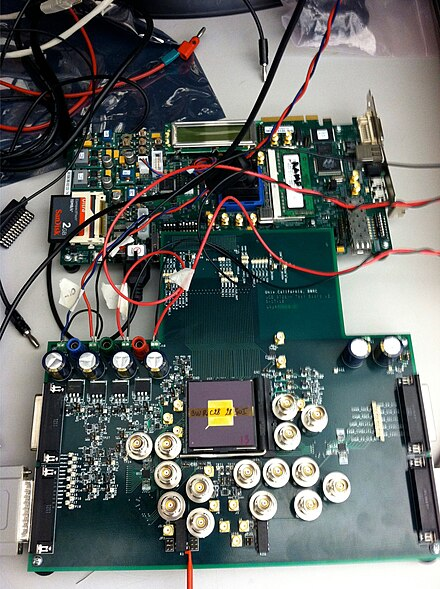

Fast forward to now, we are finally starting to see some development boards - complete, usable RISC-V systems that can be used by developers to start contributing to the RISC-V ecosystem, or porting their software over to this new architecture.

One of the manufacturers who currently provides these dev boards is DeepComputing, the manufacturer behind the Framework RISC-V board.

Before we dive into DeepComputing, though, I would like to talk about today's sponsor -- nobody. Or, you.

Who is DeepComputing?

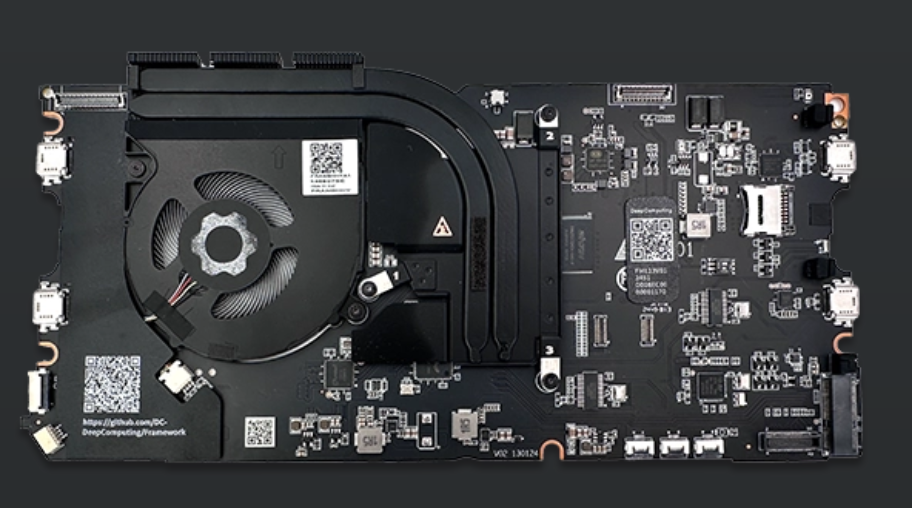

DeepComputing is a Hong Kong-based company that was founded in 2022 for the goal of pioneering RISC-V technology. Their Framework Laptop mainboard is not their first rodeo: the company already has quite a bit of experience in the RISC-V ecosystem, between embedded / IoT products of sorts (they even have a RC car!) and other mainboards.

Their Framework mainboard is, in fact, based around their "DC-Roma" SoC, which has been available in a separate development board for a while.

Not only that, but a similar chipset was integrated into another laptop solution that they sell, called the DC-Roma RISC-V laptop IIwhich is marketed to be first laptop in the world to ship directly with RISC-V. That project is similarly exciting, especially if you consider that Canonical, Fedora and other Linux distros have been on board the entire time to ensure it gets supported properly by their images. The Laptop II is more powerful than the Framework board, boasting twice the RISC-V cores on its SpacemiT K1 SoC, twice the RAM and at a faster transfer rate, as well as more ports. But it's also a completely different product: it's more of a regular laptop, as opposed to Framework's solution, which is more focused on modularity and repairability.

RISC-V on the Framework Laptop 13

So, we are finally ready to jump to the interesting part: How is the motherboard itself? First of all, you have to keep in mind that this is a chipset development board adapted into a more consumer-friendly form-factor. Although it is usable for basic tasks, it is still primarily meant for development and tinkering purposes, and it is really nothing special, performance-wise, compared to the more mainstream SoC's already on the market. You probably shouldn't buy this if you are expecting the snappiest performance for your daily tasks, but you probably should if you are the kind of person who wants to find out why it is not running faster yet, and help figure out how to improve it.

The CPU is a quad-core chip with a frequency of up to 1.5 GHz with its own Imagination GPU, combined with a pretty small 8 GB of soldered-down DDR4 memory, and... a 64 GB MicroSD card as far as storage goes. Once again, this is not going to win any performance benchmark, but it will get you running RISC-V on a consumer laptop that you can totally take to the library and prepare your next exam on - and that's incredibly cool.

Connectivity wise, things are a little closer to the more established counterparts out there: the Type-C interface supports the USB-PD 3.0 protocol for charging at a maximum of 60 W, DisplayPort 1.4 video output allows you to use this motherboard together with an external 4k monitor with no issues, all with USB 3.2 or USB 2.0 speeds. As far as the Wi-Fi and Bluetooth, it relies on a standard PCIe m.2 2230 interface, and it ships with the Intel AX210 Wi-Fi 6e card, which is known to be one of the best-supported WLAN cards for Linux.

Aside from that, it has everything else a regular Framework mainboard has: a fingerprint reader for biometric authentication and a basic audio system with laptop speakers and a 3.5 mm headphone jack.

Software support is already pretty good: initial support for the riscv64 architecture is there since Linux kernel version 5.17, and this specific mainboard is completely supported by Ubuntu 24.04 and Fedora 41.

Additionally, as all Framework motherboards, this mainboard can be used either within a Framework Laptop 13, or using the Framework x Cooler Master case as a mini-PC, in desktop mode, without the need for owning an entire Framework Laptop to use it. This is especially useful for existing Framework 13 users, who might already have an AMD or an Intel motherboard installed, and may want to cycle between that and the RISC-V board inside their laptop, while still having the other, unused, motherboard available for use as a desktop PC. A particularly enthusiastic RISC-V users may decide that they do not need a ton of computer power on their laptop and use the RISC-V board inside of it full-time, leaving their existing Ryzen board at home as a "mini-PC" designated for heavier tasks,while most regular users will probably stabilize on keeping the Ryzen board inside their laptop for the long haul, mostly playing with the cool RISC-V development board in mini-PC mode.

Conclusion

This is exciting stuff. I genuinely think what is happening with RISC-V is a very positive and thrilling development, certainly one of the things we should be happy and excited about, although we are living in increasingly troubled times. Personally, I hope I will be able to get my hands on this marvel of innovation sometimes soon - but what I hope the most is that we will see a day where this technology reaches a state that is at least comparable to something like the Pine64 sooner than later. Even if it would have limited support for proprietary executables due to it being a new architecture mostly focused around the free software ecosystem, I would definitely love, one day, to be able to get away with using a RISC-V laptop for at least the majority of my light daily tasks. Great work, Framework, DeepComputing and all the amazing people behind RISC-V.